# 半導体のはなし

# 半導体の歴史

# その25 20世紀後半 超 LSI への道1980年代 DRAM における日本メーカーの台頭 その2

株式会社フローディア 代表取締役社長 おくやま こうすけ 奥山 幸祐

## ■ 1980年代における DRAM メモリセルの進化と選択 ■■

前稿まで1970年代後半から1980年代に半導体産業を日本 電気 (NEC)、東芝、日立、富士通、三菱電機などの日本の 総合電機メーカーが DRAM 製品を核にして急激に台頭し てきたことを述べた。DRAM は1個のメモリセルに1ビッ トのデータを書込むが、時間が経つと情報が消えてしまう 為に、一定の時間で読み出し、再書き込み (リフレッシュ) を行う操作が必要であり、情報を読み出す場合も元の情報 が無くなる為に読み出した直後に再書き込みが必要となる。 このため、これらの動作を効率的に、且つ、安定して、出 来る限り高速で行うための回路技術が重要であり、各世代 で改良が図られてゆく。この様な複雑な制御回路を必要と しながらもメモリ製品として最も多く量産されたのは、1 ビットの情報を書き込むセルの面積が最も小さく、1チッ プ当たりに最も多量の情報量を書き込むことができるため である。このことから、1個のメモリセルを如何に小さな 面積で実現できるかが最も重要な技術となる。1970年代後 半からの10数年間における日本半導体の躍進はこのメモリ セル技術開発を先導し、各世代の DRAM 製品を逸早く市 場投入し続けた所にある。その後、1990年代に入って、メ モリセル技術が成熟し、世代間の開発が単に高精度な製造 設備導入で可能になると、市場動向を見極めながら資本力 を集中投入できる韓国などのメーカーが台頭してくる。今 回は DRAM メモリセル技術に日本の物づくりが最も発揮 された1970年代後半からの10数年間を、当時、先導的役割 を果した日立のあゆみをひとつの例として取り上げる。本 稿を執筆するに当たり、日立、エルピーダにて1kビット から1Gビットまで DRAM の開発に関わり続けてきた清水 真二氏と、日立中央研究所にて DRAM メモリ容量素子の 絶縁膜を研究し、スタック・セルの容量絶縁膜の研究をリー ドし続けた大路譲氏から、2010年に日立返仁会が研究小史を纏められた時に執筆された原稿を提供して頂き、それらの資料や、お二人からお聞きした内容にできる限り忠実に沿って、日立での DRAM メモリセル技術の進化について触れる (以下、登場人物の敬称を略させて頂きます)。

#### ■ 1. 高容量絶縁膜の開発 ■■■

DRAMのメモリセルは1 Kbit~4kbitの時代に、3Trs型セルで始まり、4Trs型、1 Trs型と競い合って、16Kbitの時代に1Trs型に落ち着く。一方、スケーリングの考え方が確立し、ムーアの法則と同じく、3年で4倍の集積度が期待される時代となってくる。しかし、基本となる微細加工は3年で0.65倍の見通しであり、これを実現するためには、更に、セル構造の工夫による高集積化(0.65倍/3年)とチッ

清水真二

プサイズの増大(1.5倍/3年)を組み合わせて実現してゆく道筋が定着してくる。セル構造の工夫として、1 Trs 型に定着すると構造的な変更余地は少なくなり、いかに容量値をスケーリングと調和させるかが大きな議論となる。一方、大容量化で寄生容量が増大するため設計的には容量値=信号量を単純にはスケーリング(縮小)できないことが示され、微細化しつつも一定の信号量が得られるように、単位面積当たりの容量値を増大させることが重要な課題となってくる。

当時、容量絶縁膜は、最も信頼度の高いゲート絶縁膜として使われている熱酸化膜が使用されている。しかし、セルの微細化とそのための酸化膜の薄膜化を進めてゆくと、酸化膜信頼度の限界を超えてしまうことが予測され、その対応として、誘電率の大きいナイトライド膜( $\mathrm{Si}_3\mathrm{N}_4$ 膜)が候補と考えられる。 $\mathrm{1980}$ 年に、日立が世界に先駆け $\mathrm{64Kbit}$ の第二世代で容量絶縁膜としてナイトライド膜の実用化を完成させる。そして、その後、ナイトライド膜が容量膜の

標準仕様として定着してゆく。ナイトライド膜採用するに 当たり大きな課題は信頼性である。当時の DRAM の信頼 度不良の最大の要因は、この容量絶縁膜の信頼度であり、 そのため、最も清浄な Si 結晶表面を熱酸化して作る熱酸化 膜が最も信頼度的に優れていると考えられる。更に、ナイ トライド膜を採用するためには、それに伴う界面電荷等の 問題から、MOS 構造で使うことは無理であり、Si 基板側も 拡散層にして、純粋な容量構造にする必要がでてくる。こ のことは、最も清浄な結晶表面を使うのではなく、不純物 打ち込みで結晶構造が壊された拡散層を用いること、更に、 結晶面から熱酸化によって成長させた酸化膜ではなく、 CVD法で降り積もらせたナイトライド膜を使用すること、 と言う、信頼度的に見て二重にハンディをもつ構造を採用 することを意味する。従って、ナイトライド膜の採用は極 めて無謀なことと判断され、更に、膜の信頼度評価を行うと、 ナイトライド膜は熱酸化膜に比較して、形成法の違いから 初期欠陥の数も多く、絶縁破壊のモードもたちの悪いソフ トな壊れ方を示す。

しかし、最終的には、ナイトライド膜を酸化処理し、ピ ンホールを補修することでこの問題を回避することに成功 する。この成功は、技術的には相対的に小さなものであるが、 その影響は極めて大きなものと考えられる。その1つは、 それまで DRAM の最大の信頼度問題であった容量膜の絶 縁破壊不良が、これにより激減し、極端に言えば、このこ とで DRAM の商品としての信頼度が確立したと言える。 もう1つは、それまでのSi結晶表面を熱酸化膜で作らなけ ればならない、と言う呪縛を解き放ったことである。それ によって、その後の立体化セルへの道が確保されることに なる。ナイトライド膜の実用化が、日立で、いち早く成功 した背景には2つの面がある。1つは、(64Kbit で世界の TOPを取ったとか、日米逆転が起きたこと等が、ジャーナ リスティックな話題となるが、) DRAM 市場はやっと1,000 億円規模に達したところでまだ相対的には小さく、開発の 現場では担当者が実質的に自由に発想し決断できる環境に

土屋修

あったことであり、他の面は、この容量絶縁膜が、DRAM 最大の信頼度問題であり、無数の不良解析を積んできていて、必要とされる膜質に対する量産感覚が育っていたことが、早い判断を生んでいる。

清水はこのナイトライド膜の開発を研修員報告が終わったばかりの土屋修に次のテーマとして担当させている。土屋の研修員テーマは、その前段階としての、容量ゲート酸

化膜の下に N+層を形成し容量を増やすことである(Hi-C 構造)。これはシリコン基板に多量の不純物をドーピングし て形成したN+層の上に酸化膜を形成する手法であるが、 この酸化膜の信頼性が問題になる。この為に、土屋はN+ 化による容量向上と、酸化膜の信頼性低下とのバランスに 苦しむ。その解決策として清水は CVD の要素グループに は無謀だと言われるが、窒化膜を容量絶縁膜として採用す ることに決めて、土屋に検討を開始させる。土屋は CVD の要素グループからナイトライドの CVD 膜にはピンホー ルがあることを聞いていたので最初からナイトライド膜形 成後に酸化することを考える。清水は「結論的に得た容量 膜構造のポイントは、破壊しやすいが絶縁性のいい膜(熱 酸化膜)と絶縁耐性は高いがリーク電流が大きい(窒化膜) とを組み合わせ、積層膜化を図ることでリーク電流が少な く、絶縁耐性の良い膜が実現する。これが、次のタンタル 酸化膜を開発する時の指導原理になったと思っています。 それと、64K 開発前の時代に、不揮発性メモリの MNOS を 色々調べた時があり、この時、窒化膜の電流特性を調べた 経験が生きたのだと思います。」と後に振り返っている。こ の開発により、誘電率が大きく大きな容量を取れる膜とリー ク電流の少ない酸化膜とを組み合わせることで、互いの欠 陥を補う事により、高誘電率で高信頼性の膜が生まれる。 この容量絶縁膜を64kビットの第2世代に適用することで、 次の256k ビット DRAM の開発を進めやすくなり、1983年 に商品化し64kビットについで世界トップの座を得ている。 そして1MDRAMの開発に入って行く。

## - 2.3次元メモリセルの開発 - 2.3次元メモリセルの開発 - 3.3次元メモリセルの開発 - 3.3%元

この時期に開発され、現在に至る DRAM の基本構造は、1) 3次元メモリセル、2) 低抵抗ゲート電極、3) CMOS化、4) 多層配線化 (Al 2層配線化)、の4本の基本プロセスである(図.1)。1)~4) のすべてを日立が先頭を切って開発し、量産化したものであり、特に、技術的新規性と困難性の高かった、1)、2) に関しては、研究開発の段階から先頭を切り、業界をリードしている。ここではその代表例として、「3次元メモリセル技術」を、量産技術として開発・確立した観点から取り上げる。

### 2.1 3次元メモリセルの実現

1 Mbit 以降を考えると、ナイトライド膜の採用だけでは、 行き詰まることが予想される。その様な中で、「半導体のは なし19」に記載した、日立中央研究所から、スタック型と トレンチ型が提案され、実証される。それが契機となって、 DRAM セルが 3 次元セルに切り替わり、1 Mbit 以降の発 展が実現してゆく。 基本MOS 基本プロセス 配線構造 メモリ・セル 微細加工 製品

| Trib office |            |              |     |      |  |  |  |  |  |

|-------------|------------|--------------|-----|------|--|--|--|--|--|

| PMOS        | NMOS       |              |     |      |  |  |  |  |  |

| Si-gate     | Si-gate/2層 |              |     |      |  |  |  |  |  |

| Al-1層       |            |              |     |      |  |  |  |  |  |

| 3Trs        |            | 1Trs/ブレナー・セル |     |      |  |  |  |  |  |

| 10um        | 7um        | 5um          | 3um | 2um  |  |  |  |  |  |

| 1K          | 4K         | 16K          | 64K | 256K |  |  |  |  |  |

| CMOS      |       |       | CMOS      |        |       |      |  |

|-----------|-------|-------|-----------|--------|-------|------|--|

| Pollycide |       |       | Pollycide |        |       |      |  |

| AI-2層     |       |       |           |        |       |      |  |

|           | 立体化セル |       | 立体化セル     |        |       |      |  |

| 1.3um     | 0.8um | 0.5um | 0.3um     | 0.18um | 0.11m | 70nm |  |

| 1 M       | 4M    | 16M   | 64M       | 256M   | 512M  | 1G   |  |

図. 1 DRAM 技術の流れ

#### (1) スタック・セル

中央研究所からデバイス開発センターに最初に提案されたのは1978年であり、従来技術の延長で可能なスタック型のセル構造で、64Kbitの開発中の時代である。そこで、清水らは開発済みの16Kbitメモリにこのスタック型セルを実装し、スタック・セルの評価を行う。当時は、やっと酸化膜のドライエッチ技術が始まりだしたところで、poly-Siのスタック化で必要とされる、絶縁膜と poly-Si 膜の多様な加工ニーズを実現するほどには技術がまだ成熟おらず、スタック型で実装できるセル構造も単純な構造となり、評価結果は、技術的に実現可能で、特に大きな問題点は見られないが、1980年に、その当時の加工技術レベルでは、容量増大効果が小さい、との結論となる。

#### (2) トレンチ・セル

その後、1982年に1 Mbit 以降に向けて、セル構造の限界が議論される中で、中央研究所はトレンチ型のセルをデバイス開発センターに提案すると同時に、水面下でスタック型のセルを研究所内部で並行して検討開始している。研究所内部で完全に選択しきれなかった為である。トレンチ・セルは、Si 基板に穴を掘って大きな表面積を持つ容量を埋め込むという破天荒なアイデアであり、とても開発フェーズのプロセスで検討できるようなものではなかったので、研究所においてアイデア実証から開始する。

半導体技術がプレナー技術によって実現されたと言われるように、Si 結晶表面の特性を活かして確立された技術であったものが、Si 基板にデバイスを埋め込むと言うことは、Si に穴を掘ってデバイスを形成することになるので、Si 結晶技術から始まって、加工技術、熱処理技術、CVD 技術等の様々なプロセス技術に加え、計測技術、解析技術、シミュレーション技術に至るまで、半導体プロセスに関わるほとんどすべての技術を基礎から見直して、新たに創り出す技術開発を意味する。しかし、清水達が、その意味を正しく認識できたのは、この技術を開発段階に持ち込んだ1984年頃である。清水は「その意味で、このトレンチ技術の研究・開発は、その後の半導体技術の深化に非常に大きな影響と成果を与えたと考えています。その観点で、トレンチ・セ

ルを含む 1 Mbit プロセス開発が、過去40年の DRAM 開発の中で最も新しい技術を生みだした創造性豊かな開発であったと考えています | と振り返っている。

#### 2.2 メモリセル構造の進化と選択

1984年、青梅に新しく建設された開発ライン(D-2)の立上と並行して、1M 試作品による1M プロセスの開発が行われる。この1M プロセスは、先に挙げた1)~4)の新プロセスをすべて取り込んだ極めて意欲的なプロセス開発であり、日立の技術開発の高揚期を象徴している。同時に、清水らは、この課題に見通しを付けないと、DRAM の将来が厳しいという技術者の危機意識を持って進める。

1 M 開発は、二つの大きな課題を抱える。 1 つは、前述 した1)~4)のトレンチに代表されるその後のメモリ技 術の方向を決める極めてハードルの高い新技術の開発と、 もう1つは、それと関連するドライエッチなどの新技術の 導入で、そのために新しいコンセプト装置が次々と出現し 始めた時期である。清水らは武蔵工場のラインでは全く対 応できず、青梅に新ラインを立ち上げることであり、この 2つを同時並行に進めることになる。これを進めるための 開発の旗が特研体制の"D-2ラインでの1.3um 開発"となる。 この様な状況下で、清水は1M 開発という観点では、技術 的にもライン的にも大きなリスクを抱えるため、当然、バッ クアップが必要と考える。清水のグループを2つに分け、 宮沢弘幸に、トレンチ構造を用いた1MビットDRAMを 青梅で開発する担当を任せ、前記の土屋修に、従来型のプ レナー構造で256KPSRAM(疑似 SRAM)の開発を武蔵で 担当させている。清水自身は開発の責任者として青梅常駐 し、当時、武蔵工場で SRAM の開発、試作を担当していた 目黒怜と長沢幸一にバックアップを依頼している。PSRAM (擬似 SRAM) は、内容的には DRAM で、動作を自動リフ レッシュにして外から SRAM 的に見せているもので、プロ セス的には DRAM である。清水は「DRAM としてもプロ セス技術としても大きく転換する時代に、将来に繋げる技 術開発の流れを如何に早く作るかと言う点と 1 MDRAM と 言うビジネスの競争でどう成功させるかと言う点のせめぎ 合いでした。一般には、ビジネス競争が強調されますが、

振り返って見ると技術の転換期に将来に繋げる技術開発の 仕組みを確立したことの方が重要であったと思えます。あ の1Mトレンチ開発の時に、その後に繋がる様々な技術チャ レンジがなされ、その後の本当の発展に繋がったと感じて います。個々のプロセス技術だけでなく、検査・分析・シミュ レーション等の技術がこの時の不良解析から育って行きま した。」と振り返っている。

メモリセル選択は結果的には、トレンチ構造では当時問 題になり出していた a 線によるソフトエラーが、基板にア ンテナを建てた形になるセル構造のため、致命的な不良率 になることが予測され、1985年に実用化を見送っている。 代わりに、逆櫓として256KPSRAMで実装評価していた従 来のプレナー・セルの改良型に切り替えている。従来構造 の延長で実用化が可能になった理由は、①目標チップサイ ズを大きくし、条件を緩和したこと(性能より時期を優先 させた)、②両極性の使い方(1/2 Vcc プレート)により、 実効電界が半分になり薄膜化が可能となったことの2点で ある。トレンチ開発以外のテーマも含めて非常に多くの新 しい課題にチャレンジしている段階での、この製品化計画 の変更で、開発部隊にとって厳しい状況となる。課題は、 トレンチ開発をきっかけに拡大・深化し始めた技術開発の ポジティブな流れとこのままでは1M-DRAM ビジネスに 遅れをきたすという事業判断の中で、その両立を図ること である。

これを受け、日立では1 M-DRAM 量産立ち上げと並行して、4 M-DRAM 開発のために、研究所から事業部までの開発部隊を青梅地区に集結させる特別プロジェクト(MH-PI(メモリ必勝プロジェクト))を発足する(1986年)。

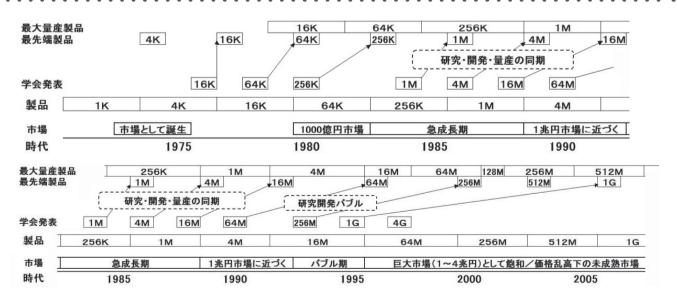

この開発プロジェクトを発端として、時間のかかる技術開発と市場への時間競争である量産化の双方を両立させるために「開発 PJ」と「量産化 PJ」を並立させる仕組みがその後確立されてゆく。これによって、その後の世代において、先行して研究開発が行われるようになり、DRAM の研究開発が加速されていく一方、図2に示すように量産と研究の間の距離が離れてしまうと言う弊害も発生して行く。

MH-PJ の開発リーダーは、それまで中央研究所で1973年から伊藤清男らと DRAM 設計の研究を担当してきた下東勝博である。下東は研究所内部で1982年からトレンチ・セルの逆櫓としてスタック・セルの検討を水面下で進めてきている。

この時に、根幹技術となる多結晶(ポリ)Si ゲート間の容量絶縁膜の研究を担当していたのが、当時、中央研究所で絶縁膜の研究を行っていた大路譲である。大路はそれまでファイナルパッシベーション膜に適用するプラズマ CVD

ナイトライド膜の形成技術の 研究を終えた所である。プライド膜の ズマ CVD ナイトライド院に フッ素を添加することで、膜中に含有する水素量(浮遊化の 中に含有する水素型(浮遊化の 中に含有する水素の 中に含有する水素の 中に含有する水素の 中に含有する水素の がののSFETの さいのである。この研究の 目途を付けた後に担当したの がスタック・セル用の容量絶 縁膜の研究である。

字 大路譲

大路はスタック・セルの容

図. 2 時代と製品

量絶縁膜として、清水、土屋らが64kでプレナー・セル用 に開発した、ナイトライド膜を形成した後に酸化する手法 を更に進化させ、多結晶シリコン上に大幅に絶縁膜を薄膜 化にした ON 膜の適用を検討し、1984年に下東らが作った 400k ビットメモリセル TEG で特性評価できるレベルまで 完成させている。しかしながら、4 Mb DRAM の製品歩留 を考慮した欠陥密度仕様に対し、この研究所で作った TEG で確認できる欠陥密度の下限が大きすぎ、判断が出来ず、 大量のデータで製品適用可能性を判断するしかなく、SiO<sub>2</sub>/ Si<sub>3</sub>N<sub>4</sub> 2層膜のプロセス最適化と適用判断も、MH-PJ に引 き継がれてゆく。このプロジェクトの中で大路は、プロセ ス部隊のリーダーである八木と共に、如何に大量なデータ を取得しようとも、市場に出した何百万個の製品の10年間 の信頼性との間には超えようの無い開きがあり、メガビッ ト以降のメモリ開発の難しさに最後まで気を揉むことにな る。この事から、研究開発の手法もこの時から変わり始める。 新しい材料の導入は、基本技術の完成だけでは製品技術と して適用判断が出来ず、大量の統計的データと関連するプ ロセス要因の考慮が求められ、これから後、様々な知恵の 結集と大規模試作が必要になってゆく。

1982年時点で目標とした容量絶縁膜の厚さはSiO<sub>2</sub>に換算 して10nm を切るまで薄膜化することである。多結晶シリ コン上に形成した熱酸化膜は、単結晶シリコン表面に形成 した熱酸化膜に比べて極めてリーク電流が大きい。これは 結晶粒ごとに異なる結晶方位や、結晶粒界の存在、多結晶 シリコン膜表面の凹凸などが、熱酸化膜の膜質劣化の原因 になっているためである。最初に検討したのは清水、土屋 らが開発した SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>の3層絶縁膜であるが、3層 構造では薄膜化が難しく、そこで Si<sub>3</sub>N<sub>4</sub>単層膜の検討も進め るが、バンドギャップの小さい Si<sub>2</sub>N<sub>4</sub>単層膜ではリーク電流 を抑えることが困難なことは明らかである。そこで、バン ドギャップの大きい SiO<sub>2</sub>膜を下敷きにした CVD-Si<sub>3</sub>N<sub>4</sub>膜と の2層膜でそれらの問題の解決を図ろうとする。しかし、 多結晶シリコン表面に形成した熱酸化膜は膜質の著しい劣 化を引き起こすことは明らかであり、必然的に2層膜の構 造として、多結晶シリコン上に直接 Si<sub>3</sub>N<sub>4</sub>膜を CVD 成膜し、 その表面を熱酸化した $SiO_2/Si_3N_4$ 2層膜を選択することに なる。当初は CVD 法で成膜した Si<sub>3</sub>N<sub>4</sub>膜をベースにして本 当に欠陥密度が小さく、信頼性の高いキャパシタ絶縁膜を 作成できるのか不安が付きまとうが、意外にも試作したキャ パシタ TEG に欠陥は少なく、リーク電流も低いという結果 に驚く。SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>2層膜の長所は、清水、土屋のグルー プも考えたことでもあるが、CVD-Si<sub>3</sub>N<sub>4</sub>膜表面を酸化する 時に、もしSi<sub>3</sub>N<sub>4</sub>膜に欠陥があった場合でも、この酸化処理 が、その欠陥を修復するという点にある。この考え方は、 後年、大路が再び DRAM メモリセルの絶縁膜の研究に携 わり、世界で初めて Ta<sub>2</sub>O<sub>5</sub>膜の実用化を可能にすることに

なるが、その時の研究にも繋がってゆく。この特徴のお蔭で、 SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> 2層膜を容量絶縁膜としたスタック・キャパシ タは欠陥密度が低く、作り易いキャパシタになる。ここで SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> 2 層膜と述べているが、実は Si<sub>3</sub>N<sub>4</sub>膜を CVD 法 で成膜する際に、多結晶シリコン電極上に2nm 程度の自 然酸化膜が成長する。この為、実際には SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> 3 層膜と言った方が正しく、ここでは積極的な熱酸化をして いないという意味で2層膜と称している。しかし、この自 然酸化膜が、上層の SiO<sub>2</sub>層と同様にリーク電流の低減に重 要な役割を果たしていることも大路らは明らかにしている。 スタック・キャパシタへのSiO<sub>2</sub>/Si<sub>2</sub>N<sub>4</sub>膜の採用成功は、 その後の DRAM セル構造の流れに向けた大きな転換点と なる。その後、更なる容量絶縁膜の薄膜化の要請に沿って、 高誘電率絶縁膜(Ta<sub>2</sub>O<sub>5</sub>やBST)の開発、多結晶シリコン に変わる金属電極の開発、フィン構造やチムニー構造など より、複雑なスタック・キャパシタ構造の開発などに進ん でゆく。

下東らはこの  $SiO_2/Si_3N_4$ 容量絶縁膜を用いたスタック・セル用の DRAM 回路の研究を一年間続け、1985年のMH-PJ へと繋げている。これらの中央研究所での水面下での研究と、清水らが 1 M 開発で経験した技術開発の課題を 4 M 開発に継続的に引き継ぐことが、次の 4 M での開発経過に大きな役割を果たしてゆく。また、1985年に、富士通が  $SiO_2/Si_3N_4$  2 層膜を用いたスタック・セルの実用化で先行しており、 1 M に搭載している。これに追いつき、自社でスタック・セルを実用化できる絶縁膜の実現を求められる。

4 M の世代で加工技術や前記の容量絶縁膜後術の進化に よりスタック・セルの実現性が見えてくると、トレンチ型 とスタック型のどちらのセルを選択するかが議論になって くる。トレンチ型は、α線問題の影響が非常に大きく、基 本的な構造改良が必要とされる。即ち、構造的にトレンチ 形状を使うが、容量機能はその中に埋め込む基板プレート 方式が必要となる。このことは、1/2 Vcc プレート方式 が使えず実効的に容量面積が2倍必要になること、構造的 に難度の高いプロセスになることから、4Mでの実現は困 難と判断し、プレナー型かスタック型か?の判断となる。 一方、スタック型は、トレンチ型での検討で問題となった セル間リークやα線ソフトエラーなどのデバイス特性面で 優位であることが認識される(記憶ノードの接合面積が最 少になり、それに比例してα線ソフトエラーも向上する。 このため Hi-C 構造化も必要でなくなり、高濃度接合に伴 うリーク電流の問題も軽減される)。中央研究所での水面下 における1982年からの3年間のスタック型の研究と、デバ イス開発センターで清水らが行った1980年の256Kでのス タック型の評価で課題となった加工技術(当時困難であっ た) も 1 M 開発で技術進歩していることから、 4 M で必要

とされる高度な構造も可能と判断する。一方、世界的には、 日立のトレンチ・セルの提案に刺激され、各社がトレンチ・ セル開発に注力する中、前述のように1985年に富士通が1 Mを容量絶縁膜に ON 膜を用いたスタック型で実現させて いる。

4 M でのプロト試作評価の結果、1 M での基盤技術の進 歩でスタック・セルの評価は良好な結果を得る。逆櫓とし て検討していた(チップサイズ大のまま、早期市場投入を 目的とした)プレナー・セルは限界が見えていたので、4 M でのセル選択はスタック型に比較的早期に絞り込んでい る(1986年)。清水は「4Mが、結果的に他社に先行して 市場で優位に立てた(1987年末に世界に先駆けサンプルを 出荷し、量産化でも TOP を維持できた) 背景は、このセル の選定過程で現れたように、1Mの時代の深い検討経験で 早期に的確な判断ができたためであります(当時の最大の 競争相手であった、NEC、東芝、TIに比較して)。技術開 発の面では、1M 開発で着手した様々な新規性の強い技術 課題が大きな壁を乗り越え、技術の成熟化・高度化に向か いだす時期に達していました。そのことは、この頃になる とこれら技術課題に対応できる装置が揃い出したことでも 感じられました。」と4Mの成功を振り返る。

16Mの世代になると東芝などが4Mの世代でトレンチ方 式の製品化に成功していることもあり、4Mの時以上にト レンチ型かスタック型かの選択について再び議論される。 基盤となる技術は1Mプロトの開発で裾野広く着手され、 かなり習熟してきていたため、セル構造の将来性が重要な 課題となる。1988年に両者ともに技術的には可能と判断さ れ、製品に近い形での評価が必要となり、並行開発でスター トしている。この時期には、トレンチ型もスタック型も最 初に提案された構造とは大きくかけ離れた極めて複雑な構 造が必要とされてきている。理由は、セル面積も電圧もス ケーリングされるのに対して、蓄積電荷量がほとんどスケー リングされる見通しがなく、容量形成にスケーリングのし わ寄せが集中して来るためである。そして、将来的にもそ の方向が変わらないことが認識される。一方、両者とも構 造の複雑さには大差がないほどにそれぞれ複雑な構造に なっていく。予想される将来像は、針のように細長くなる 容量部を、基板に埋め込むか、地上に建てるかの違いとなる。 トレンチ型では、容量部を埋め込むためメモリ部も周辺回 路部分も共通の同じ平坦面となり配線行程がより容易にな り、問題点は穴内の容量部形成に集中される。スタック型 では、容量部が積み上がったメモリ部と何もない周辺回路 部分に大きな段差が生じ、平坦性確保のため、深いコンタ クト穴の形成が必要となる。セルの性能差は大差なく、む しろ量産技術面での選択が重要となり、相対的に穴内の特 殊技術が必要とされるトレンチ型が不利と1989年に判断す る。それ以降(64M以降)、その判断は変わることなく、 スタック型のみで開発を進めて行くことになる。1989年になると各社の16Mの学会発表が出揃い、スタック型による4Mでの日立の先行の影響から、それまでのトレンチ型中心から、一転して、スタック型の発表が主流となる。

#### 2.3 64M 以降のメモリセルの進化と選択

64M以降からは、各社とも両方を比較することはなくなり、スタック型なりトレンチ型なりをそれぞれ追求するようになる。理由は、両構造とも技術的には可能であり、一方、それぞれの積み上げた技術が高度になり容易には変更できなかったためである。技術的な難度は、トレンチ型の方が大きかったので、結果的には、トレンチ型は、IBM、東芝、シーメンスの3社のみとなり、更には、この3社は1992年に共同して開発する体制へと移行してゆく。

この問題は更に、尾を引く。巨大な装置産業でもある半導体では、量産は装置に依存し、量産技術も装置に依存する。いい技術が量産に耐えるためにはそれを実現するいい装置が必要となり、いい装置が開発されるためには、その装置が大量に売れる見込みがないと開発されない。トレンチ型は、より特殊な技術条件を必要とするため、この障害が大きく、3社共同開発として声を大きくしたが、装置側から見た市場規模は小さく、最終的には、2007年にトレンチ型が放棄されることになる。

その後のもう一つの側面は、DRAMの TOP が変わる原 因となったことであると清水は指摘している。「1 M/4 M/16M の時代までは日米の H、N、T、TI、IBM 等が技術 と市場を牽引していたが、1996年の DRAM 市場のバブル 崩壊以降、主役として Micron や韓国勢が優勢となります。 その理由として、投資戦略の問題が指摘されていますが、 それには技術的な背景があると思います。この時代を経て、 「メモリセルは方向性が定まり、より高度な加工技術ができ れば、より小さな構造が実現できる(それが量産的には難 しそうに見えるにしろ)」と判断されるようになっていまし た。後発メーカーである研究部隊を持たないこれらのメー カーは、新しい技術的可能性を追求する道ではなく、効率 的な量産実現の道を選んで、そこへ集中投資しました。一方、 研究部隊を持つ従来のメーカーは、量産化での解決よりも、 セル問題の技術的解決をより志向しました。巨大化した DRAM 市場で生き抜くためには、巨大な投資による生産能 力の確保と、ますます難しくなる技術課題に比例した巨額 化する開発費との両者をどうするか?の問題になっていま した。後発メーカーは単純に割り切り、量産化技術を含む 生産投資に集中しました。先発メーカーは、開発投資負担 軽減のために共同開発へ動き、生産能力確保では生産委託 への道を選びました。結果的には、この中途半端な道が転 落への道となり、その後は、後発メーカーが市場を支配した、 と考えています。」と1990年代以降の DRAM 産業の総括を

している。

更に、「1 M/4 M/16M の時代は、例えてみれば、それまでの木造平屋作りの町から、超高層ビルが密集する都市への転換点でした。材料、工法からメンテ手法まで、実に幅広く新しいアイデアと技術が必要とされ、創り出されました。その時期に、世界の中で日立が先頭を切り開いて活躍できたことは素晴らしいことでした。それができた背景は、それだけの人材と組織を日立が持っていたからだと思います。そしてそれが実現された要因は、

- 1) 新しいアイデアが活発に提案され、それを試してみようとするチャレンジ精神が旺盛だったこと、

- 2) 意識的に先を見た組織的動きがなされ、研究から量産までの意識がそろい、認識が共通化し、様々な知恵の集結・活用ができたこと、であったと思います。」と纏めている。

挿絵 奥山 明日香

#### 参考文献

- 1) 清水真二 日立返仁会 2010 研究開発小史 第一巻「高集積 DRAM の研究開発 世界一への挑戦 10. 量産化・製品化」

- 2) 大路譲 日立返仁会 2010 研究開発小史 第一巻「高集積 DRAM の研究開発 世界一への挑戦 8. 絶縁膜イノベーション」

# 第27回 半導体の歴史

一その26 20世紀後半 超 LSI への道一 1980年代 インテルの DRAM 撤退と戦略