製品情報

製品の特徴

- AEC Q100準拠、グレード0(zero)対応可能

- CMOS プロセス完全互換

- 既存デバイスとSPICEへの影響なし

- 既存IPと設計資産の流用可能

- 低コスト

- 追加マスク 0~数枚

- 短テスト時間

テクノロジー

The Advantage of SONOS

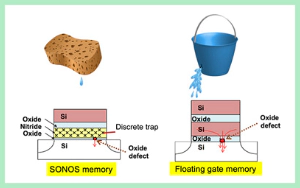

フローディアのG1及びG2は、SONOS構造を採用しており、他社が採用しているフローティング型不揮発性メモリ構造に比べ多くの利点があります。

High Reliability

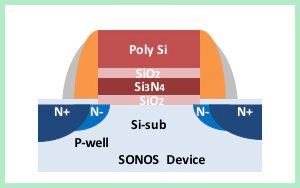

SONOS型のチャージトラップを用いた電荷保持機構は、フローティングゲート電荷蓄積型とは異なります。SONOSは、窒化シリコン膜のトラップサイトに電荷が強く結合しているため、プログラムや消去動作時のダメージによって生じたボトム酸化膜の欠陥を介した電荷のリークというものがありません。

フローディアのSONOS技術は、書き込みおよび消去動作にFNトンネル現象を採用しています。書き換え耐性は酸化膜中の欠陥が書き換え時の電流によって増加することで律速されますが、FNトンネル電流のレベルはpAのオーダーと極めて微小なため、書き換え回数の増加に対応した酸化膜損傷も極めて軽微に留まります。

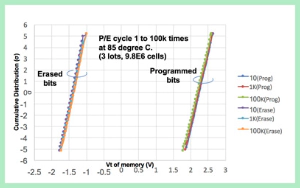

High reliability – Stable Vt

メモリセルの電位(Vt)分布は、非常に狭く安定しているのがFNトンネル電流を用いたSONOS型メモリの特徴です。そのため、書き込み/消去動作中に電位分布を確認しながら書き込み/消去作業を繰り返す、ベリファイ・プログラミングのサイクルが不要になり、テスト時間の短縮が可能です。

10万回の書き込み/消去が実行された後であっても、劣化は見られません。

また、チャネル領域全体に電子と正孔が均一に注入され、酸化物の品質は高く維持されます。

Easy to Manufacture

チャージトラップシステムとしてFNトンネリングは最適な方法と考えられます。それは製造上の欠陥があっても電荷(電子/正孔)がSiN膜中に閉じ込められて電界が弱められるからです。加えて、チャネル領域全体にわたってトンネリングすることにより、電子と正孔が均一に注入されて電界の分布も均一になるという特徴があります。

Large Programming Size enables Short Testing Time

フローディアのSONOSメモリは、FNトンネル技術を採用しているため、極めて低い電力で書き込みおよび消去が可能です。

FNトンネル技術の場合、書き込み/消去動作にホットキャリア注入を使用する従来の技術と比較して、消費電流が1/ 1,000,000になります。

1メモリセル当たりの消費電流が十分に小さいため、大きなブロックを一括してプログラムすることも可能となります。その結果チップコストの大きな部分を占めるテスト時間の短縮にも役立ち、低コスト化を実現します。

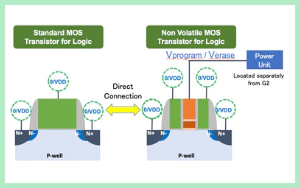

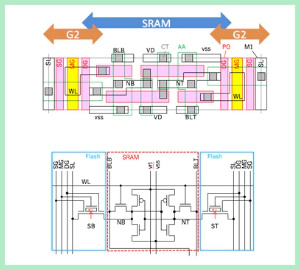

High Speed Non Volatile SRAM

ローディアのG2は、VDDでの “読出し動作”をサポートする独特な機能を備えてます。これは、フローディアだけの技術です。従来の組込み用不揮発性メモリは、通常、書き込み/消去/読出し動作中に中高電圧を必要としていましたが、 G2セルへの高電圧供給はメモリゲートに対してのみだけで、電源回路は通常メモリブロックの外部に配置されます。メモリブロック内から高電圧領域を排除することにより、メモリセルと論理回路は分離領域を持たずに隣接配置することができます。 G2セルとSRAMセルを隣接配置すると、この新しいタイプの結合セルは不揮発性SRAMとして動作します。フローディアは、G2の独特な機能を利用して、より多くの次世代アプリケーションを提供いたします。

Marriage of Logic and Flash

G2セルは、1つのSONOSトランジスタとその両側に隣接して配置された2つのスイッチングトランジスタから構成される3ゲート型トランジスタです。G2は、スイッチングトランジスタへの論理レベル電圧およびSONOSメモリゲートへの高電圧によって動作する1つの不揮発性トランジスタとして動作します。各セルへの書き込み電流が、フローティングゲート型NVMに比べて1 / 1,000,000と非常に小さいため、SONOSメモリゲートへの配線は信号線のように扱われます。

また電源回路は、チップのコーナー部などのメモリブロックの外部に配置することができます。このG2の独特な機能によりチップ設計の自由度が高まり、論理回路と不揮発性機能を組み合わせた新しい回路設計が可能になります。

Non Volatile SRAM

高速不揮発性ランダムアクセスメモリ(NV-SRAM)は、MCU、SOC、FPGAのアーキテクチャ設計を劇的に変化させると期待される夢のデバイスの1つです。

フローディアは、2つのG2セルと6トランジスタ型SRAMセルを直接組み合わせることで、非常に実用的で新しいソリューションを提供します。 RAM機能はNV-SRAMのSRAM部分によって実現され、SRAMに格納されたデータはシャットダウン/パワーダウン時にG2セルに転送され、G2セルに格納されたデータは電源投入時にSRAMに再転送されます。この新しいNV-SRAMは、非常に簡単な方法で、かつ何ら新しい材料を使用することなく高速NV-SRAM機能を実現します。

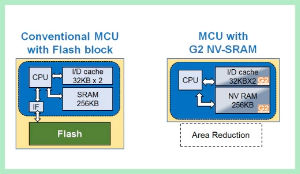

MCU with NV-SRAM

高速NV-SRAMは、MCUのメモリアーキテクチャに変革をもたらします。

専用のフラッシュブロックやインタフェイス回路は不要となり、フラッシュブロックとの間の余分な転送時間が削減できるなどの大きな利点を提供することができます。この新しいアーキテクチャを利用すれば、MCUシステムを非常にきめ細かくスリープモードにして消費電力を制御でき、電源投入後には即座にシステムをスタートさせることもできるようになります。

![株式会社フローディア [Floadia]](https://floadia.com/jp/wp-content/themes/floadia/assets/images/floadia.svg)