LEE Flash G2

製品情報

LEE Flash G2, Flash beyond Flash

LEE Flash G2(G2)は、他のフラッシュIPにはない独自の機能を提供する革新的なフラッシュIPです。

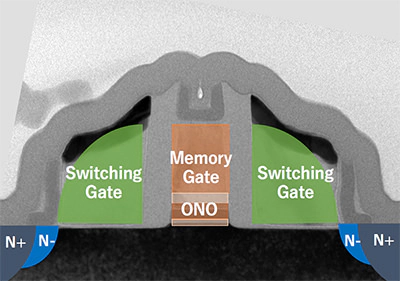

G2は、単純なSONOSメモリであるLEE Flash G1(G1)の側面にスイッチトランジスタを配置した構成になっています。

追加コストが最小限というG1の特長を維持しながら、読み出しに高電圧を必要とせず、またメモリセルとロジック回路の間に分離領域がないためレイアウトが容易という特長があります。

G2の非常に特殊なVDD動作アーキテクチャにより、G2フラッシュ・セルを標準ロジック回路に直接接続できます。そのため、SRAMなどのロジック素子の不揮発性化が可能になり、革新の新たな可能性が開かれます。

さらに、数メガバイトまでの大容量メモリを必要とするアプリケーションに費用対効果の高いフラッシュソリューションを提供します。

また、既存のPDKおよびSPICEモデルが利用可能であり、標準のCMOSプロセスプラットフォームにそのまま搭載できます。

※G2開発中

Major Features

- 論理回路との直接接続、既存の揮発性論理回路の不揮発化

- 読み出し動作に高電圧を印加しないため、分離領域が不要で柔軟なレイアウトが可能

- 過酷な自動車環境に対応した高温動作および高いデータ保持特性

- 極少消費電力の書き換え

- テスト時間とベーク時間の短縮によりテストコストを削減可能

- 追加マスク最大4枚

- 標準CMOSプロセスのSPICEモデルに影響がない為、既存のIPと設計資産を再利用可能

仕様例

| Item | Spec |

|---|---|

| Process platform | 55BCD |

| Memory Size | 128K-Byte(1M-bit) |

| P/E Cycles | 100K |

| Supply Voltage | VDD 1.2V±10% |

| VCC 2.5V~5.5V | |

| Additional Masks | 4 |

| Operation Temperature(Tj) | -10~175℃ |

| Data Retention | 10years@175℃ post PE 10K |

論理回路との互換性

SONOSは、窒化シリコン膜に電子をトラップすることでメモリ機能を実現するデバイスであり、そのデータ保持寿命は、酸化膜および窒化シリコン膜の膜厚および膜特性の最適化によって制御することができます。データ保持特性は、10年以上@200℃を確認しています。

大容量メモリ

小さなメモリセルとコアトランジスタで構成された周辺回路は小面積のIPを実現します。

テスト時間が短縮可能

G2は、FNトンネル技術により、書き込みおよび消去電流が極めて低く、ホットキャリア注入を使用する従来の技術と比較して、消費電流は1 / 1,000,000です。これによりテストコストの大部分を占めるテスト時間を短縮できます。

低コスト

テスト時間の短縮: 2つの理由から大幅にテスト時間を短縮することが可能です。

- 書き込み/消去時の消費電力が非常に小さいため、テスト時にはメモリマット全体を一度に書き込み/消去することができます。従来の書き込み方式のように小さなセクションを何度も消去してメモリマット全体を書き込み/消去する必要がありません。

- 書き込み後のメモリのVt分布は均一のため、書き込みベリファイが不要かつ書き込み動作が一回で完了するため、書き込み時間が短縮されます。

ベーク時間の短縮

フローディア独自のメモリ構造は、メモリセルの寿命予測を簡素化し、スクリーニングのためのベーク時間を短縮することができます。

追加マスク(4枚)

G2は、標準CMOSプロセスで4枚の追加マスクしか必要としないため、チップ上に不揮発性メモリ機能を実装するための高価なマスクコストを削減できます。従来のソリューションでは、通常10枚以上の追加マスクが必要とされます。

既存の設計資産の再利用

通常のフラッシュIPと異なり、フローディアのフラッシュIPはロジック・トランジスタのSPICEモデルには影響せず、開発された既存の設計資産を再利用することができます。

![株式会社フローディア [Floadia]](https://floadia.com/jp/wp-content/themes/floadia/assets/images/floadia.svg)