LEE Flash G1

G1

产品信息

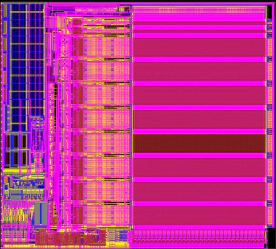

LEE Flash G1,best fit eFlash to BCD process

LEE Flash G1(G1)因采取简单的SONOS结构,可以随制程微缩至40nm工艺节点,同时也可达到车规电子的温度及质量要求。G1是一款高经济效益的中等容量闪存。除此之外,即使使用G1, 逻辑晶体管和SPICE模型的特性也不会改变,因此为一般CMOS制程所设计的IP是可以被重复使用的

Major Features

- 读写功耗低

- 追加光罩最多2至3片

- 不会改变标准规格CMOS制程上的SPICE模型,可重复使用现有的设计及IP

- 测试与制程时间短,有助于降低成本

规格示例

| Item | Spec |

|---|---|

| Process platform | 130BCD |

| Memory Size | 64 Kbyte |

| Data Bus(Main) | 32 I/O |

| P/E Cycles | 100k |

| Supply Voltage | VDD 1.5V±10% |

| VCC 2.5V~5.5V | |

| Additional Masks | 2~3 |

| Operation Temperature(Tj) | -40~175℃ |

| Data Retention | 10years@175℃ post PE 10K |

High Temperature Operation

G1 数据保留特性高达 @200°C 确认超过 10 年

Large Programming Size enables Short Testing Time

G1因使用FN穿隧技术,在执行写入/抹除动作所消耗的电力非常微小,与一般使用热载子注入来达到写入/抹去动作的技术相比,穿隧技术只需使用其1/1,000,000的电流即可。这样可帮助缩短测试时间,同时也有利降低成本。

Low Cost

Short Test Time: G1 achieves very short test time for two reasons.

- G1所需要的测试时间很短,主要有两个原因,其中之一为执行一次写入/抹去所需的电力极小,所以可让测试人员一次便可测试整个内存芯片,不同于传统的嵌入式闪存只能小单位写入/抹去,G2所需的整体测试时间很短。

- 另一个原因为G1编程的Vt分布因为很集中,所以可降低多次编程和验证的需求,因此不需要复杂的步骤便可完成编程操作,进而大幅缩短编程的时间。

Short Baking Time

富提亚科技独有的内存结构,可简化预测内存位寿命的过程,这样可缩短晶圆公司筛选晶圆时间。

2-3 Mask adder

G1使用在标准规格的CMOS上时只需要追加2至3片的光罩,可以降低因开发非挥发性嵌入式闪存时所需要的高额光罩成本。若是一般的非挥发性内存的话,通常在先进制程上需追加10片以上的光罩。

Re-use of existing IP asset

与一般的快闪IP不同,富提亚科技的快闪IP因不影响逻辑晶体管及SPIEC模型的架构,所以可以重复利用制程上既有的IP。

Track Record

| Manufacturing status | Item |

|---|---|

| Mass Production | 130nm, PSMC 90nm |

| Available on | TSMC 130BCD+ |

| Under development | PSMC 80BCD, SMIC 90BCD, UMC 110BCD |

![富提亚科技 [Floadia]](https://floadia.com/kn/wp-content/themes/floadia/assets/images/floadia.svg)