LEE Flash G2

G2

产品信息

LEE Flash G2, Flash beyond Flash

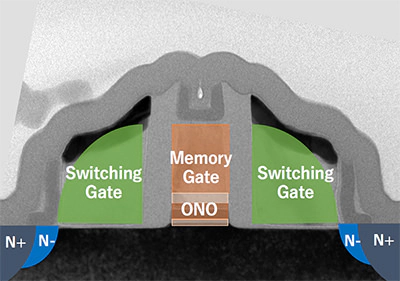

LEE Flash G2(G2)提供一般嵌入式闪存IP所没有的独特功能,是跨世代创新的快闪IP。G2是在由单纯SONOS架构制成的G1侧面安装开关晶体管的构造。G2维持G1追加光罩所需成本较低的特性,另外因读取时不需高电压,在内存位与逻辑电路之间也不需放置分离区域,有利于电路布局作业。

G2因为拥有非常特殊的VDD架构,快闪位可直接连接逻辑电路。因此可以使SRAM等逻辑组件达到非挥发性的可能,开创非挥发内存的新世代。此外,对于在应用程序等方面需要极大内存容量的客户,G2是一个高经济效益的解决方案。读取时不需高电压,可省去分离区域利于电路布局作业

※G2正在开发中

Major Features

- 读写功耗低

- 测试与制程时间短,有助于降低成本

- 追加光罩最多4至5片

- 不会改变标准规格CMOS制程上的SPICE模型,可重复使用现有的设计及IP

规格示例

| Item | Spec |

|---|---|

| Process platform | 55BCD |

| Memory Size | 128K-Byte(1M-bit) |

| P/E Cycles | 100K |

| Supply Voltage | VDD 1.2V±10% |

| VCC 2.5V~5.5V | |

| Additional Masks | 4 |

| Operation Temperature(Tj) | -10~175℃ |

| Data Retention | 10years@175℃ post PE 10K |

Logic Compatibility

因为写入及抹除动作的高电压不会被施加于扩散层,所以所有的读取电路都由标准规格的核心晶体管所构成。因此与外围的逻辑电路保持良好的兼容性,如同SRAM一样,可与逻辑电路混合。

High Speed by VDD operation

藉VDD達到高速動作

Large Memory Capacity

大容量記憶體

Large Programming Size enables Short Testing Time

G2因使用FN穿隧技术,在执行写入/抹除动作所消耗的电力非常微小,与一般使用热载子注入来达到写入/抹去动作的技术相比,穿隧技术只需使用其1/1,000,000的电流即可。这样可帮助缩短测试时间,同时也有利降低成本。

Low cost

Short Test Time: G2 achieves very short test time for two reasons.

- G2所需要的测试时间很短,主要有两个原因,其中之一为执行一次写入/抹去所需的电力极小,所以可让测试人员一次便可测试整个内存芯片,不同于传统的嵌入式闪存只能小单位写入/抹去,G2所需的整体测试时间很短。

- 另一个原因为G2编程的Vt分布因为很集中,所以可降低多次编程和验证的需求,因此不需要复杂的步骤便可完成编程操作,进而大幅缩短编程的时间。

Short Baking Time

富提亚科技独有的内存结构可简化预测内存位寿命的过程,这样可缩短晶圆公司筛选芯片时的时间。

4 Mask adder

G2使用在标准规格的CMOS上时只需要追加4至5片的光罩,可以降低因开发非挥发性嵌入式闪存时所需要的高额光罩成本。若是一般的非挥发性内存的话,通常在先进制程上需追加10片以上的光罩。

Re-use of existing IP asset

富提亚科技独有的内存结构可简化预测内存位寿命的过程,这样可缩短晶圆公司筛选芯片时的时间。

![富提亚科技 [Floadia]](https://floadia.com/kn/wp-content/themes/floadia/assets/images/floadia.svg)