LEE Flash ZT

Product Info

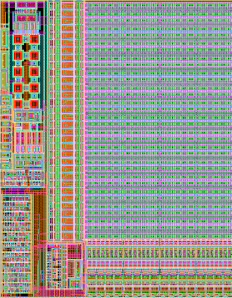

LEE Flash ZT, Zero Additional Mask MTP

LEE Flash ZT (ZT) achieves automotive grade temperature and quality grade.

Perfect fit for trimming and parameter storage in Sensor, Power and Analog ICs especially for automotive applications.

It also achieves low cost implementation due to its very short test time and baking time while you need Zero additional mask or process step in manufacturing.

It supports process nodes down to around 40nm and P/E cycle up to 10K times.

Major Features

- Supports high temperature and long retention life time for severe automotive requirement.

- Low power in Program/Erase operation for power critical applications.

- Short Test and Bake time to reduce chip cost.

- Standard CMOS process for re-using existing design and IP.

- No additional mask required for easy implementation.

仕様例

| Item | Spec |

|---|---|

| Process platform | 180BCD |

| Memory Size | 512 Bytes(4K bits) |

| P/E Cycles | > 100k |

| Supply Voltage | VDD 2.5V~5.5V |

| Additional Masks | 0 |

| Operation Temperature(Tj) | -40~150℃ |

| Data Retention | 20years@-40~150℃ |

High Temperature Operation

ZT can support 20 years of retention at 125°C. ZT has track record in supporting Automotive quality.

Large Program Size enables Short Testing Time

ZT uses FN tunneling technology to achieve extremely low power in program and erase.

It consumes 1/1,000,000 times current, compared to conventional technologies which use hot carrier injection for program/erase operation.

This also helps reducing testing time, which dominates large portion of the chip cost.

Low Cost

Short Test Time: ZT achieves very short test time for two reasons.

- Extremely low power in program/erase allows tester to program/erase the whole memory mat at once, compared to conventional solution program/erase smaller sections for many many times to program/erase the whole memory mat.

- Sharp Vt distribution in programming will eliminate the requirement for multiple programming and verification, so that programming operation always completes at one time, not in multiple steps, to dramatically reduce programming time.

Short Baking Time

Floadia’s unique memory architecture simplifies Life Time Prediction of the memory cell, which allows chip company to screen devices with shorter baking time.

Zero Mask

ZT requires no change and no additional mask on standard CMOS process, reducing expensive mask cost to implement NVM feature on your chip.

Field Programmability

Floadia’s ZT allows system company to program NVM when they ship end system product, or even while the system is in the field and running, to adjust trimming/parameter setting.

Track Record

| Manufacturing status | Item |

|---|---|

| Mass Production | in several Japanese IDM, HHGrace 180BCD |

| Under development | in several Japanese IDM |